The FACETS Hardware[]

Using Wafer Scale Integration

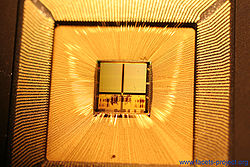

(description and larger image)

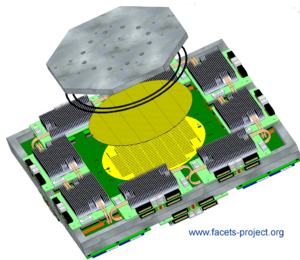

(FACETS stage I hardware system)with bond-wires (larger image)

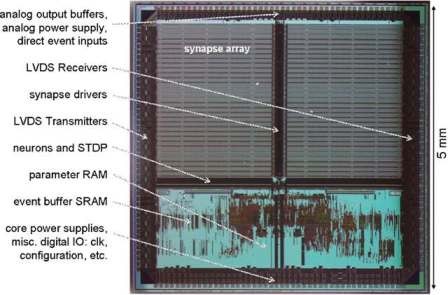

The FACETS hardware will be implemented as very large-scale VLSI-based neural circuits that emulate substantial fractions of the brain. As such, it will be based on a novel computing paradigm radically different from the Turing approach which forms the successful basis of contemporary IT systems. The new paradigm makes use of the massively parallel, complex and ongoing dynamics observed in brain activity. Thus, a detailed structural (connection pattern, neuronal diversity) and functional (dynamic states of activity, plasticity) characterization of cortical circuits is a prerequisite to establish theoretical models of the computing concepts realized in the brain that can in turn be transferred into requirements for the hardware realization.

(Electronic Vision(s) Group, Heidelberg)

The proposed hardware systems will feature a high degree of configurability, the possibility to read-out and monitor ongoing activity, and a high operation frequency. In particular, this will allow to study experimentally the very different time domains from individual spike generation over short term plasticity to long term learning, development, and possibly even evolution.

The speed of the hardware will permit to bridge the huge time gap between the above mechanisms (milliseconds to years): A relative speed-up of 100.000 can be achieved and will compress time-scales of a year to a few minutes. Therefore, this hardware is expected to serve as a valuable and flexible future research tool for neuroscience. Among other things, artificial systems of this kind will help to reduce the need for experiments carried out with living neural tissue.

(Electronic Vision(s) Group, Heidelberg)

More images are available here.