1st year results from the "Neural Hardware at the Network Level" workpackage (WP 7)[]

First generation of FACETS stage I hardware Spikey I passes initial tests[]

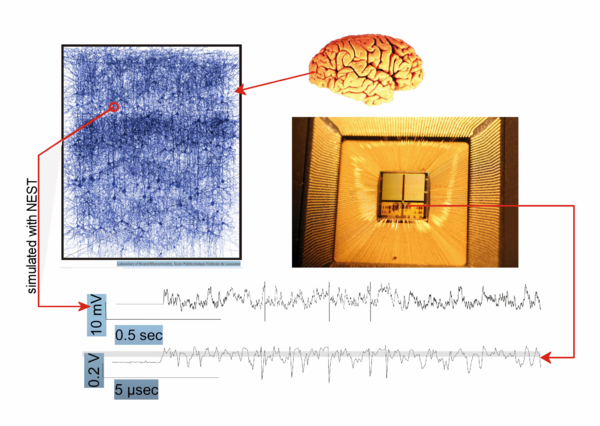

With the working system a first comparison between the hardware and the expected biological result (here represented by a software simulation with the NEST simulator) has been done. A detailed description is available as deliverable D15 Equivalence report with the first generations of FACETS hardware from WP6 and WP7. A single arbitrarily selected "neuron" on the chip has been fed with randomly generated Poisson distributed spike trains from both inhibitory and excitatory "synapses". The same setup has been simulated with the NEST software implementing the integrate-and-fire model. The input for the synapses is generated using numerical extensions for the language Python and thus is interpretable by both the Python based interface to the hardware and by the NEST simulator. The resulting membrane potential trace is very similar.

(larger image of the Spikey I chip)

In the experiments some deficiencies of the first design have been identified and an improved second version of the chip (Spikey II) has been submitted for production. The circuits used on the chips and lessons learned from the experiments with it provide the important background for the design of the FACETS stage II hardware.

Further experiments with the stage I hardware will include multiple Spikey chips communicating with each other. These experiments are necessary to test the communication protocols to transmit spike time information across chip borders.

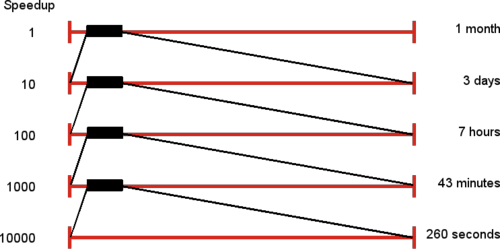

Speedup[]

The speedup factor from hardware to biology was estimated to be in the order of . With this speedup factor of 10000 a simulation which covers 1 month of biological time will only run for 5 minutes in real time.