FACETS hardware on the network level (WP7) year 2[]

During the second year of FACETS, the device tuning of an enhanced version of WP7's highly accelerated neuromorphic hardware (Stage I) was pushed further. The software framework for a powerful and convenient operation reached a level of project-wide usability by closing the gap to the FACETS experiment description meta-language.

Spikey II[]

An improved version of the FACETS stage I hardware ("Spikey II"), which had been submitted during the first year of FACETS, was received back in the second year and proved to solve the deficiencies of the first version. With this new chip, a lot of effort has been invested to specify, calibrate and control its analog functionality.

|

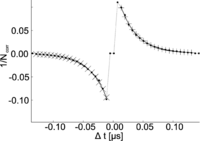

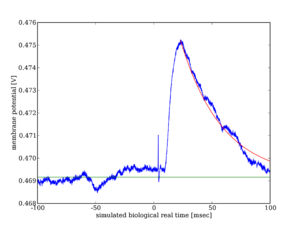

| Figure 1: spike-timing dependent plasticity (STDP) curve measured directly on a hardware synapse of the SPIKEY II chip (enlarge) |

As an example, the figure 1 shows a so-called spike-timing dependent plasticity curve, measured directly on a hardware synapse. Such curves capture the relationship between the time difference of action potentials occurring in neuron A and neuron B and the resulting strengthening or weakening of the synapse connecting A and B. The aim of this work is to be able to precisely translate neuron and synapse parameters of established models, which are normally numerically calculated by dedicated software simulators, to corresponding hardware configurations. A translation of such parameters which achieves a high precision behavior correspondence between the numerical approaches and the hardware operation is an essential part of porting existing experiment classes to the hardware.

This will allow for the exploitation of the FACETS stage I hardware's most compelling feature, its high speed (factor to times faster than biological real time, speedup). Many experiments which are well established within the computational neuroscience community could for the first time be performed in a statistics-intensive manner and thus lead to new results. New kinds of self-organization experiments and exploration of ultra-long-term learning will become possible due to the hardware's speed and its implemented plasticity.

Publication

Schemmel, J., Gruebl, A., Meier, K. and Mueller, E.: Implementing Synaptic Plasticity in a VLSI Spiking Neural Network Model in Proceedings of the 2006 International Joint Conference on Neural Networks (IJCNN'06), 2006, IEEE Press fulltext

PyNN - Integration[]

|

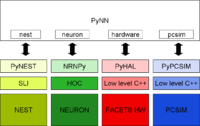

| Figure 2: A schematic view of the PyNN software architecture (enlarge) |

Since most neural network software simulators and also the hardware have all their own specific user interfaces, a meta experiment language called PyNN (http://neuralensemble.org/PyNN) has been developed within FACETS, allowing for unified and exchangeable setups, including parameters, dimensions, data types and analysis. See the schematic on the right for an illustration of PyNN being an interface to different back-ends. The FACETS hardware was integrated into this meta framework, making the ongoing effort towards precise convergence between the hardware behavior and the implemented model's numerical simulation easier.

Publications

Brette, R., Rudolph, M., Carnevale, T., Hines, M., Beeman, D., Bower, J.M., Diesmann, M., Morrison, A., Goodman, P.H., Harris Jr., F.C., Zirpe, M., Natschläger, T., Pecevski, D., Ermentrout, B., Djurfeldt, M., Lansner, A., Rochel, O., Vieville, T., Muller, E., Davison, A.P., El Boustani, S., and Destexhe, A.: Simulation of networks of spiking neurons: a review of tools and strategies in Journal of Computational Neuroscience (2007) 23(3):349-98 fulltext.pdf

Bruederle, D., Gruebl, A., Meier, K., Mueller, E. and Schemmel, J.: A Software Framework for Tuning the Dynamics of Neuromorphic Silicon Towards Biology in Proc. of IWANN 2007, San Sebastián, Spain, June 2007, Springer LNCS 4507, pp. 479 - 486 fulltext

|

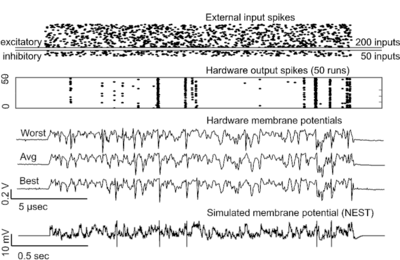

| Figure 3: Comparison between a simulation with the NEST software and the output from the SPIKEY hardware (enlarge) |

Comparison software simulation - hardware[]

Figure 3 illustrates a comparison between a software simulation and the hardware output. Since the hardware is subject to electronic noise, the generated output spikes of 50 runs of the same experiment have been plotted, showing that, statistically, the hardware reproduces the desired output well.

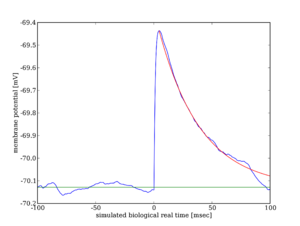

The figures below compare so-called post-synaptic potentials (PSPs), i.e. the average influence of an action potential running into a neuron's synapse on its membrane potential. The left figure shows a simulated PSP, the right one a PSP measured in hardware.

Software-simulated post-synaptic potential (PSP) (enlarge) |  Post-synaptic potential measured on the chip (enlarge) |

This picture shows a simple graphical user interface (enlarge) which allows to interactively run experiments in a very fast loop. For example, the user can manipulate the stimulus for a given network while he is immediately observing the effect of the change on the output spikes of a subset of the network's neurons.

Publications

Schemmel, J., Gruebl, A., Meier, K. and Mueller, E.: Implementing Synaptic Plasticity in a VLSI Spiking Neural Network Model in Proceedings of the 2006 International Joint Conference on Neural Networks (IJCNN'06), 2006, IEEE Press fulltext

Schemmel, J., Bruederle, D., Meier, K. and Ostendorf, B.: Modeling Synaptic Plasticity within Networks of Highly Accelerated I&F Neurons in Proceedings of the 2007 IEEE International Symposium on Circuits and Systems (2007) abstract