WP6: Neural hardware at the cell level[]

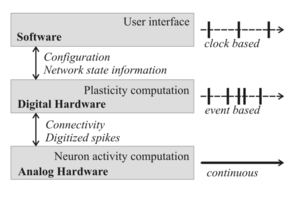

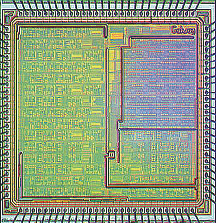

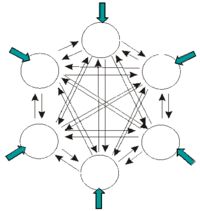

The objectives of this work package are the design and exploitation of a simulation platform based on VLSI circuits that simulate the activity of adaptive neural networks, using conductance-based models (Hodgkin-Huxley formalism). The research group 'Engineering of neuromorphic systems' at ENSEIRB/University Bordeaux 1 is in charge of designing successive generations of custom VLSi circuits[1] (ASICs[2]) and associated simulation platforms of spiking neural networks. The ASICs circuits compute in biological real-time the activity of neural elements using a complex conductance-based model (Hodgkin-Huxley formalism). The models parameters describe cortical neurons with diverse spiking/bursting activities. The ASICs are integrated on a simulation platform, where they can be organized as a neural network with an adaptive all-to-all connectivity. The platform is optimized to run in real-time temporal plasticity algorithms such as STDP (Spike-Timing Dependent Plasticity) or other Hebbian rules. The platform is used in FACETS as an efficient (computation speed, integration) tool for the exploration of the cortical cells models and plasticity algorithm in small networks. |

| ||||

|

| ||||

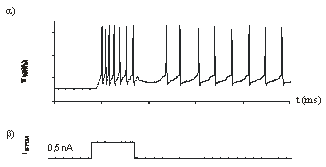

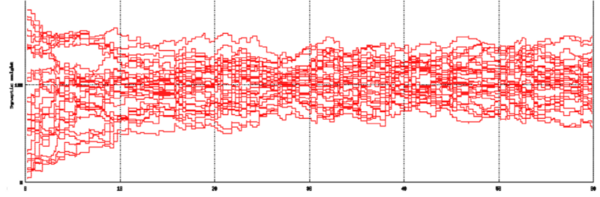

Figure 4: Demonstration of the platform performances

| |||||